## ELECTRODEPOSITION OF PbSe NANOPARTICLES ONTO N- AND P-Si WAFERS AND INTO NANOPOROUS SiO<sub>2</sub>/Si TEMPLATE

Yu.A. Ivanova, D.K. Ivanou, E.A. Streltsov, A.K. Fedotov

Belarusian State University, Leningradskaya st. 14, 220050 Minsk, Belarus kosarevay@mail.ru, Iv Dm Kon@tut.by

Due to its properties ( $E_g = 0.27$  V) PbSe is in a current use for IR electronic device manufacturing. Producing of PbSe/Si heterostructures is of great practical interest as Si is a basic material for modern electronics. PbSe deposition into nanopores in SiO<sub>2</sub> layer on Si wafer (SiO<sub>2</sub>/Si system) is important since the structures based on nanoporous SiO<sub>2</sub> and silicon wafers could be transitive between traditional silicon-based electronic devices and nanoelectronic ones [1]. Many methods are used for PbSe/Si heterostructures formation: MBE, thermal evaporation in vacuum, liquid-phase epitaxy, pulsed laser deposition, etc. Today the electrochemical methods for chalcogenides deposition onto different substrates are being successfully developed [2]. The electrochemical approach does not require vacuum, high temperatures, expensive equipment and provides an accurate control of product composition and structure. Also, electrodeposition is an unique technique for template synthesis: deposition occurs only into the pores that have an electric contact with substrate [3].

We report on successful preparation of PbSe/Si heterostructures as well as PbSe nanoparticles in porous  $SiO_2/Si$  system by electrodeposition technique. PbSe particles with sizes from 70 to 150 nm were cathodically deposited at ambient conditions onto silicon wafers with different types of conductivity (n- and p-Si) and into nanoporous  $SiO_2/Si$  template from  $0.1 \text{ M HNO}_3 + 50 \text{ mM Pb}(NO_3)_2 + 1 \text{ mM SeO}_2$  solution.

In the case of n-Si substrate PbSe deposition takes place at potentials less than flat band potential ( $E_{fb}$ ) of silicon substrate. It was found out that monophase C-PbSe deposit with composition close to the stoichiometric could be obtained at rather narrow potential range (from -0.43 to -0.45 V vs.  $Ag|AgCl|KCl_{sat}$ ). These potentials are more negative than equilibrium potential of lead reduction ( $E_{Pb}^{2+}/P_{pb}^{0} = -0.38$  V). However bulk Pb deposition was not observed. It was shown that on the first stages of PbSe nucleation bulk Pb and Se simultaneously deposited onto Si and chemically interact resulting in PbSe nanoparticles formation. Provided PbSe is presented on n-Si surface the overvoltage of bulk Pb reduction increases. Further growth of PbSe deposit is realised due to Pb UPD and Se OPD onto n-Si/PbSe heterostructure. At potentials E = -0.38 - -0.41 V the deposit contains a large excess of amorphous Se while at  $E \le -0.47$  V bulk lead deposition occurs. The illumination does not significantly exert upon PbSe electrodeposition onto n-Si.

PbSe deposition onto p-Si takes place at potentials E < +0.1 V only under illumination due to photoelectrons generated in silicon substrate. The stages of PbSe deposition onto p-Si includes simultaneously Pb and Se deposition onto Si followed by their chemical interaction. The deposits obtained in the wide potential range (from -0.20 to -0.50 V) are characterized by the same element and phase composition and represent C-PbSe (a =0.612 nm) with Pb:Se ratio ~0.9:1.

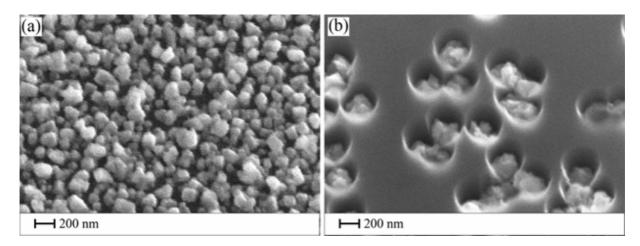

Being electrodeposited both onto *n*- and *p*-Si PbSe forms cubic-shaped particles uniformly distributed on the substrate. Typical SEM patterns of PbSe deposited onto Si are given on Fig 1a.

Photoelectrochemical properties of PbSe/n-Si and PbSe/p-Si were studied. Cathodic deposition of PbSe onto n-Si is irreversible – barrier is formed on n-Si/PbSe interface. Anodic oxidation of PbSe on n-Si is observed only under illumination when the photoholes are formed in silicon substrate. Being electrodeposited onto p-Si, PbSe undergoes anodic oxidation in the dark and under illumination as well. Both for PbSe/n-Si and PbSe/p-Si

heterostructures anodic stripping of PbSe does not proceed completely – a part of Se-rich phase is left on Si electrode and protects PbSe from oxidation.

Electrodeposition of PbSe into nanoporous  $SiO_2/Si$  template was realized at E=-0.43 V for both types of Si substrates.

To produce nanoporous  $\mathrm{SiO_2/Si}$  template,  $\mathrm{SiO_2}$  layer was thermally grown on n-Si (100) and p-Si (111) substrates at  $1100^{\circ}\mathrm{C}$  during 10 h in oxygen atmosphere. The initial thickness of  $\mathrm{SiO_2}$  layer was found to be  $0.9 \pm 0.1~\mu\mathrm{m}$ . Then the samples were irradiated by scanned beams of 350 MeV  $^{197}\mathrm{Au^+}$  ions with fluence of  $5\cdot10^8~\mathrm{cm^{-2}}$  to produce latent ion tracks in silicon oxide. Pores were formed under selective chemical etching of the irradiated  $\mathrm{SiO_2}$  layer in dilute HF. It caused the formation of pores randomly distributed over the surface and looked like truncated cones in shape. The pores diameter was controlled by etching time and varied from tens to hundreds nm.

Electrodeposition of PbSe into porous  $SiO_2/p$ -Si system was carried out under illumination. For both types of templates the deposition occurred only into the pores, deposition on insulating  $SiO_2$  layer was excluded. The degree of pore filling depended on the duration of deposition. The techniques used in the work permitted obtain a  $SiO_2/Si$  template with all the pores uniformly filled with PbSe nanoparticles (Fig 1b).

## **References:**

- [1] D. Fink, A.V. Petrov, K. Hoppe, W.R. Fahrner et al, Nucl. Instr. Meth. Phys. Res., **218** (2004) 355.

- [2] E.A. Streltsov, N.P. Osipovich, D.K. Ivanou, in Focus on Surface Science Research / Ed. Charles P. Norris. Nova Science Publishers (2005) 1.

- [3] I.U. Schuchert, M.E. Toimil Molares, D. Dobrev, J. Vetter, R. Neumann, M. Martin, J. Electrochem. Soc., **150** (2003) C189.

## **Figures:**

Figure 1. SEM patterns of PbSe electrodeposited at E = -0.43 V from 0.1 M HNO<sub>3</sub> + 50 mM Pb(NO<sub>3</sub>)<sub>2</sub> + 1 mM SeO<sub>2</sub> solution onto Si wafer (a) and into porous SiO<sub>2</sub>/Si template (b).